開発受託

FSNIP

10ミクロンピッチの接合技術 FSNIP

AIやIoT等の新たな成長市場に牽引され進化し続ける半導体チップは、多機能化・高集積化とともに外部出力端子数が指数関数的に増大しています。この動向に対応するためコネクテックジャパンは、10ミクロンピッチの接合技術 FSNIPを開発いたします。

開発コンセプト「5G製品を超小型化する」

- 1

既存技術の課題を打開

- 2

世界初となる

FSNIPを開発 - 3

小型・コストダウン

限界を打破

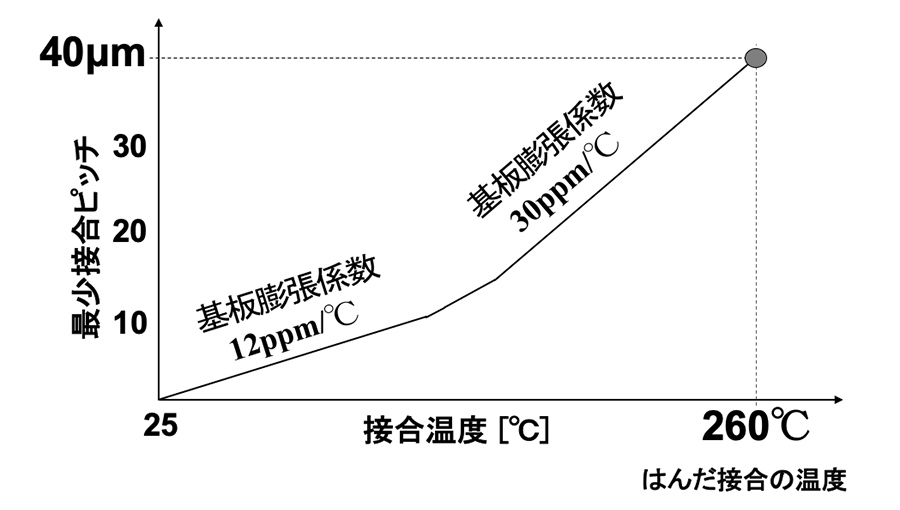

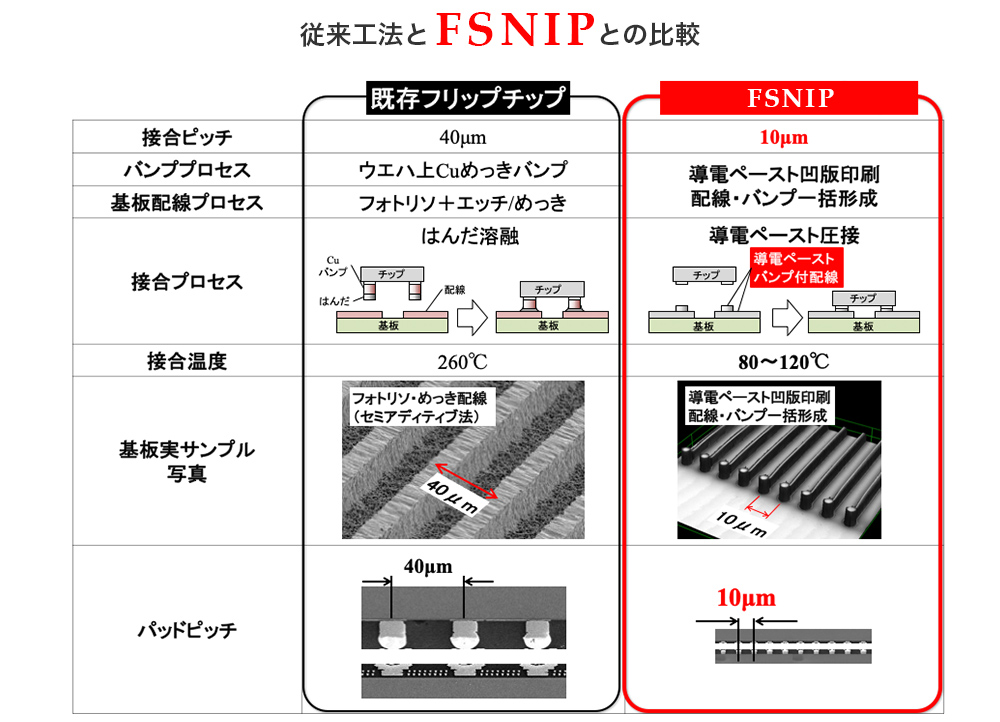

従来の接合温度と最小ピッチ

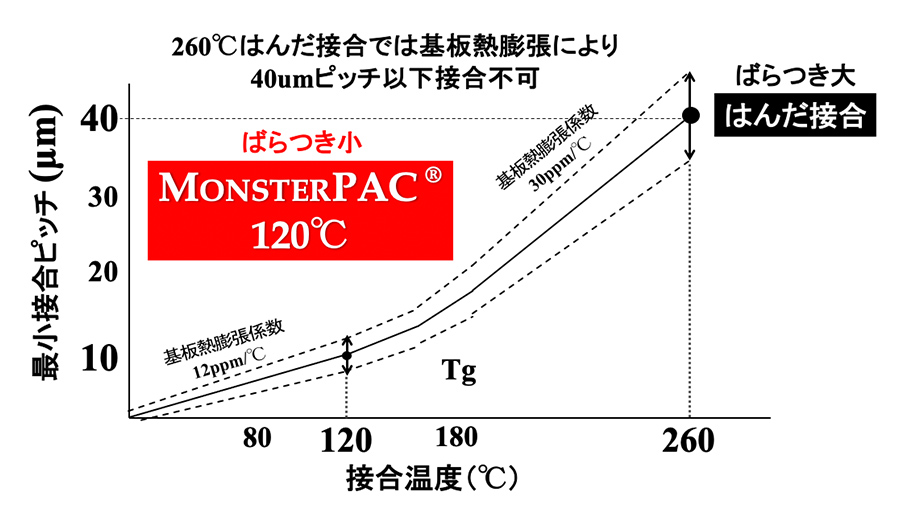

半導体前工程の配線ルールはどんどん微細化が進み、チップサイズは小さくなりますが、現在の技術ではパッドピッチの微細化に限界があるため、パッドピッチがチップ実装面積を支配し、パッケージは小さくなりません。はんだの接合温度が260℃であるため、基板の熱膨張係数から最小接合ピッチは40ミクロンが限界となるからです。

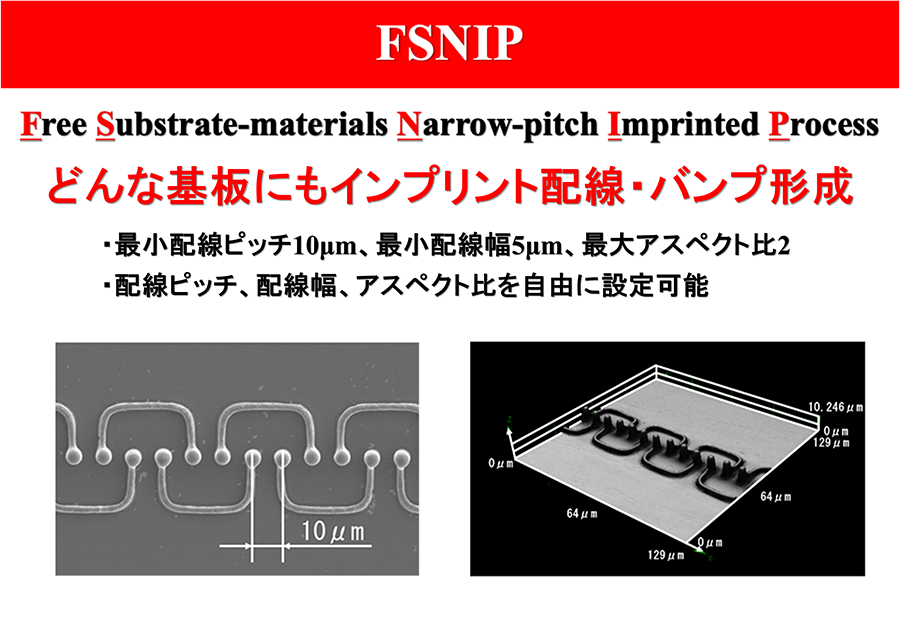

世界初のバンプ/配線ピッチ10ミクロンを実現します

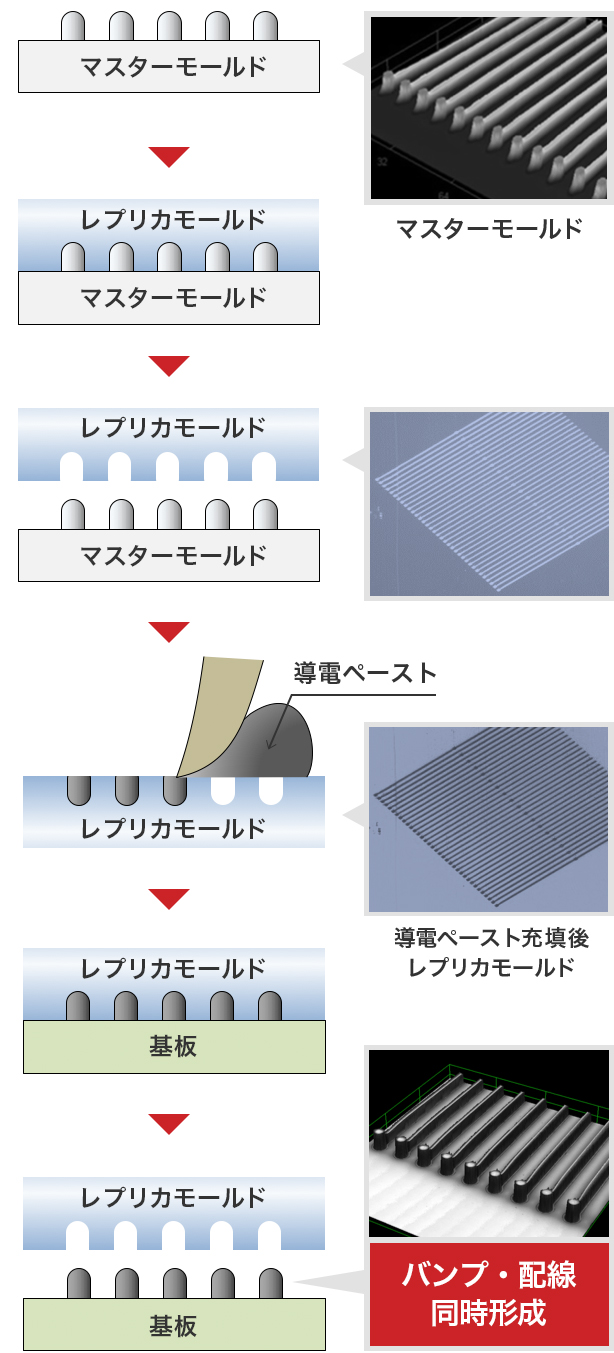

コネクテックジャパンが開発を進めているMONSTER

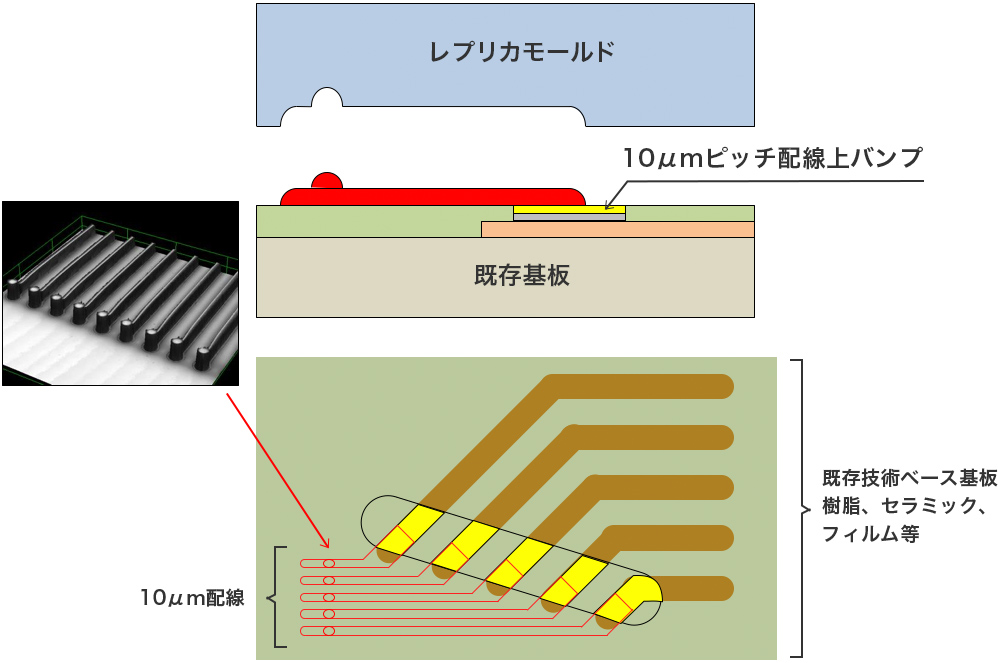

PAC®10㎛は、低温焼成導電性ペーストと、レプリカモールドを用いた凹版印刷法により、世界初のバンプ/配線ピッチ10ミクロンを実現します。

世界初10ミクロンピッチ配線・バンプ同時形成プロセス

既存配線基板への10ミクロン配線形成

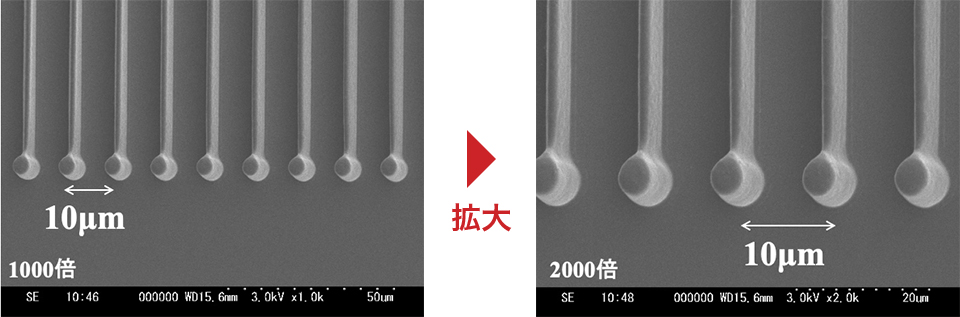

10ミクロンピッチライン・バンプ一括転写結果